# SDM: Sharing-enabled Disaggregated Memory System with Cache Coherent Compute Express Link

Hyokeun Lee<sup>+</sup> Kwanseok Choi<sup>\*</sup> Hyuk-Jae Lee<sup>\*</sup> Jaewoong Sim<sup>\*</sup>

\*North Carolina State University \*Seoul National University

#### **Outline**

Introduction

Motivation

- SDM: Sharing-enabled Disaggregated Memory System

- CXL-compatible Designs

- Evaluation

Conclusion

#### **Outline**

Introduction

Motivation

- SDM: Sharing-enabled Disaggregated Memory System

- CXL-compatible Designs

- Evaluation

Conclusion

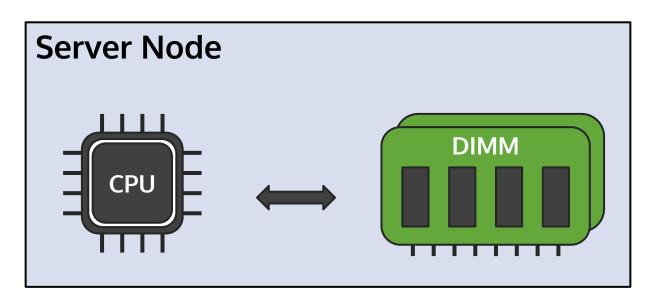

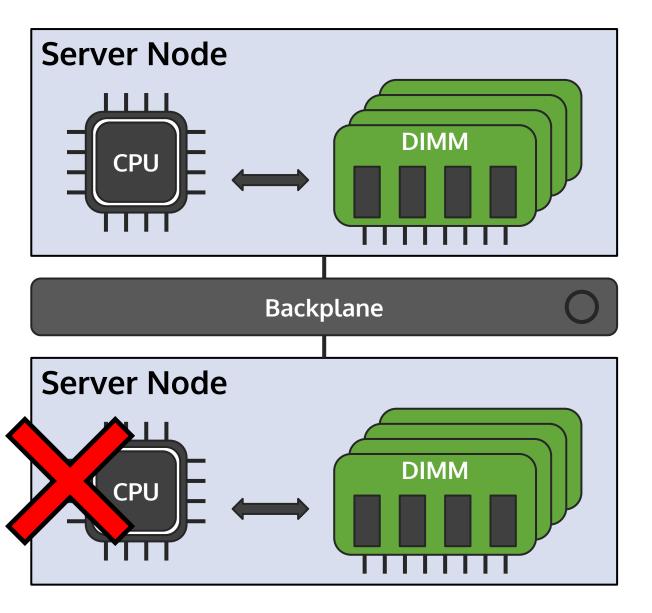

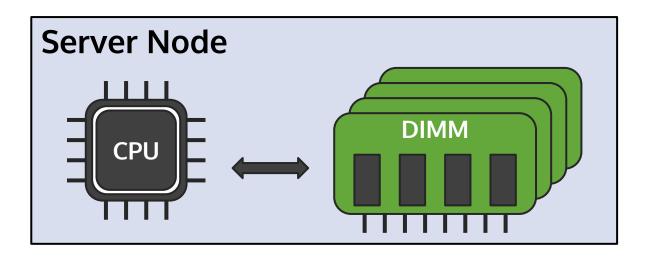

#### **Demand for Large Memory Capacity**

#### More DIMMs within the node?

Limited # Pins

#### More DIMMs within the node?

Limited # Pins

More DIMMs within the node?

Limited # Pins

More DIMMs within the node?

Limited # Pins

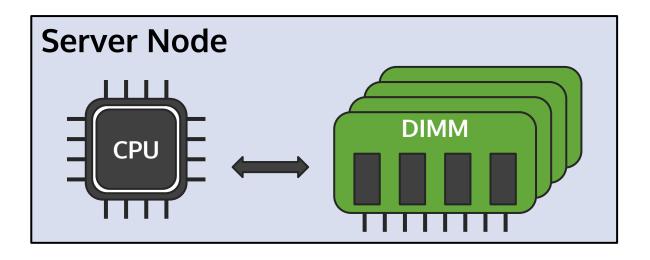

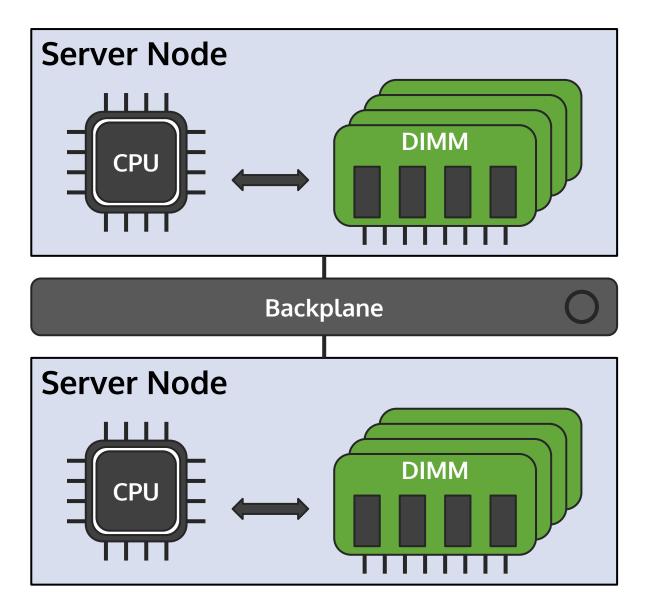

Integrate more server nodes?

More DIMMs within the node?

Limited # Pins

Integrate more server nodes?

More DIMMs within the node?

Limited # Pins

#### Integrate more server nodes?

Underutilized Cores

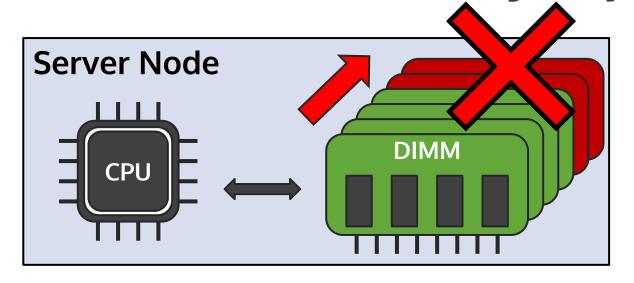

#### More DIMMs within the node?

Limited # Pins

#### Integrate more server nodes?

Underutilized Cores

More DIMMs within the node?

Limited # Pins

Integrate more server nodes?

Underutilized Cores

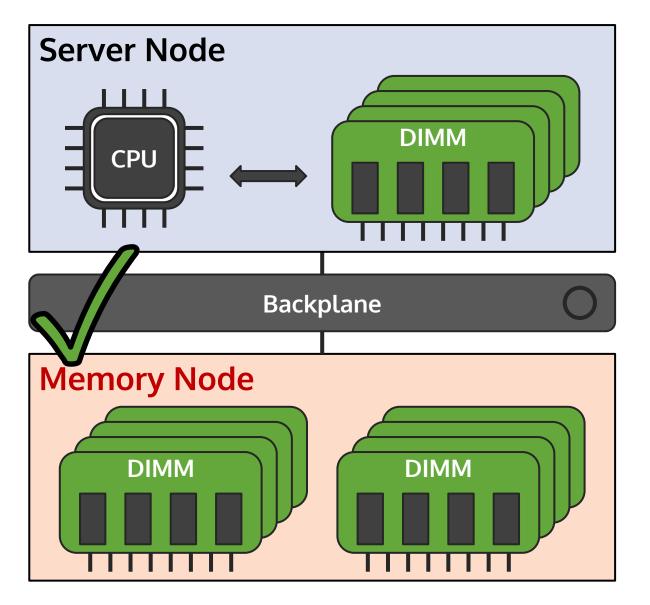

#### Solution:

**Disaggregated Memory!**

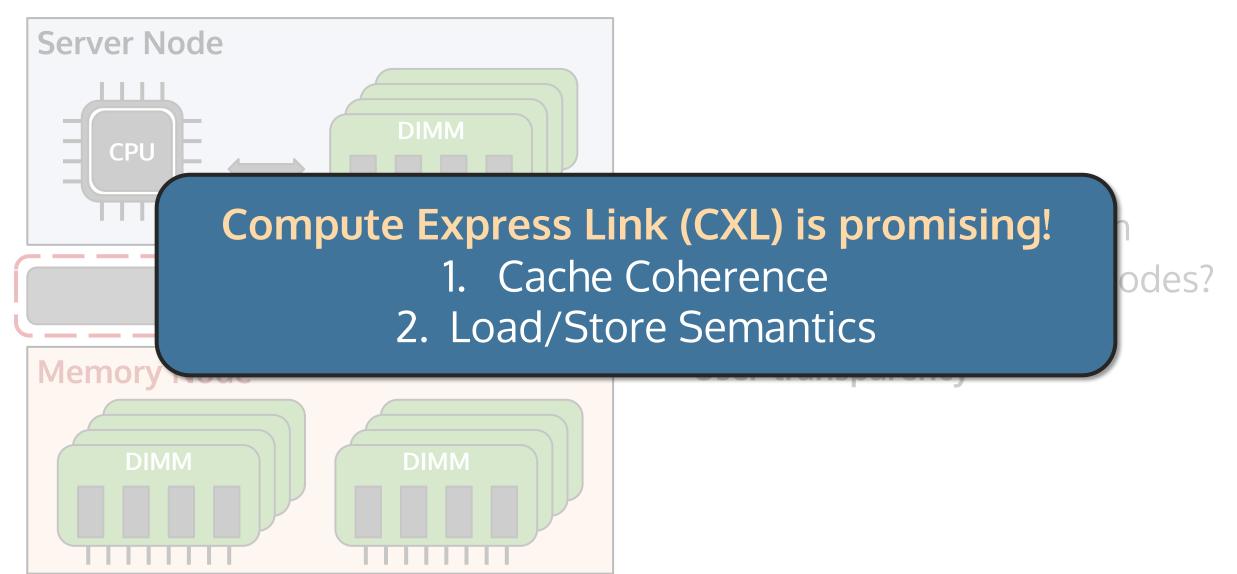

- **Q**: **Communication** between server nodes and memory nodes?

- Low latency

- User-transparency

|                   | RDMA                    | CXL                  |

|-------------------|-------------------------|----------------------|

| Low-latency       |                         |                      |

|                   | Software-stack Overhead | Cache Coherence      |

| User-transparency | RDMA API                | Load/Store Semantics |

#### **Outline**

Introduction

Motivation

- SDM: Sharing-enabled Disaggregated Memory System

- CXL-compatible Designs

- Evaluation

Conclusion

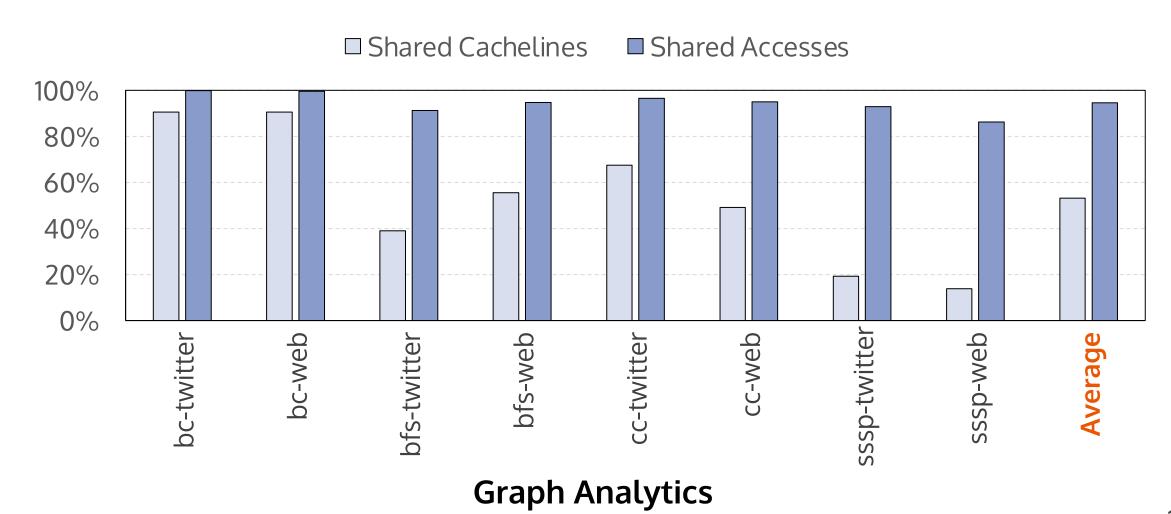

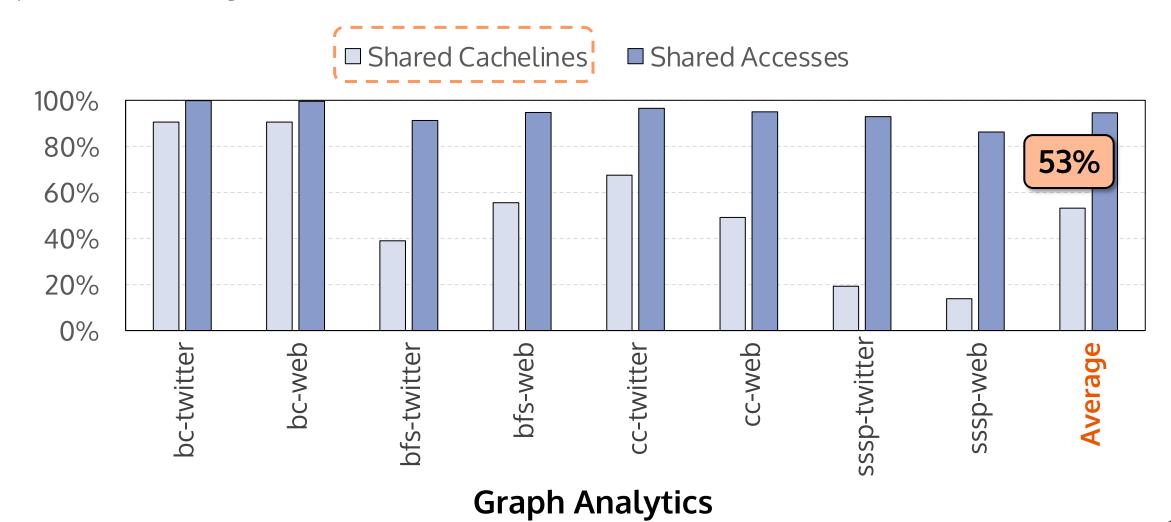

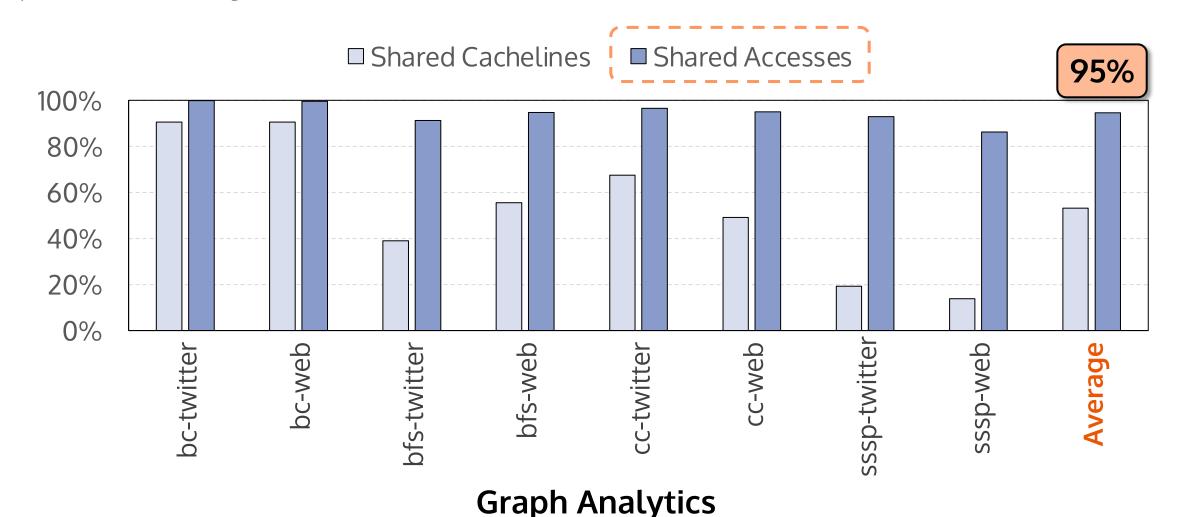

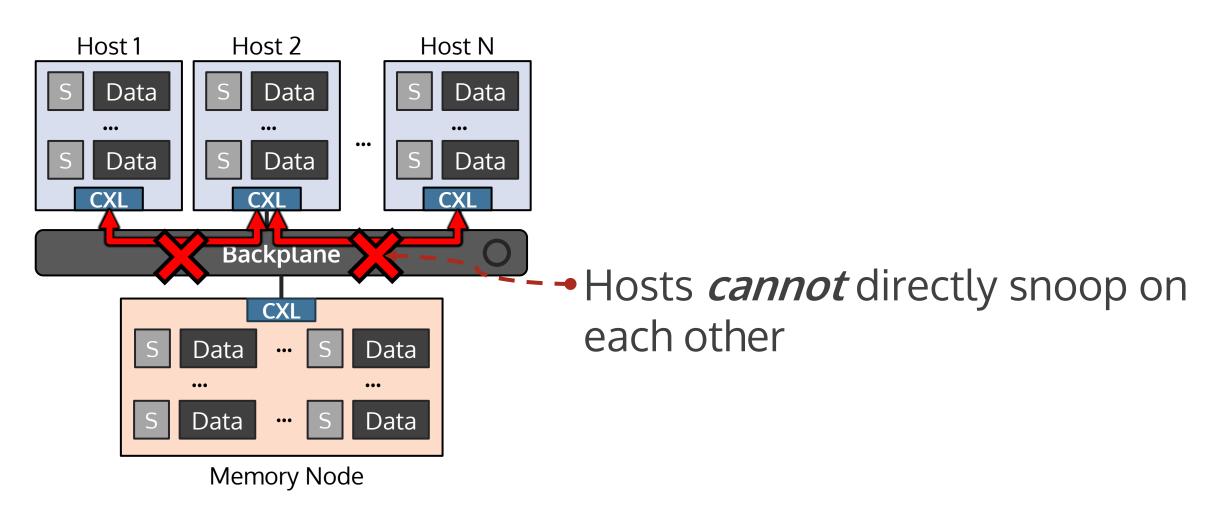

## **Multi-Host Data Sharing Opportunity**

Q: How many cachelines are shared across hosts?

## **Multi-Host Data Sharing Opportunity**

Q: How many cachelines are shared across hosts?

## **Multi-Host Data Sharing Opportunity**

Q: How many times are the shared cachelines accessed?

#### Goal 2: How to design a multi-host coherence control flow?

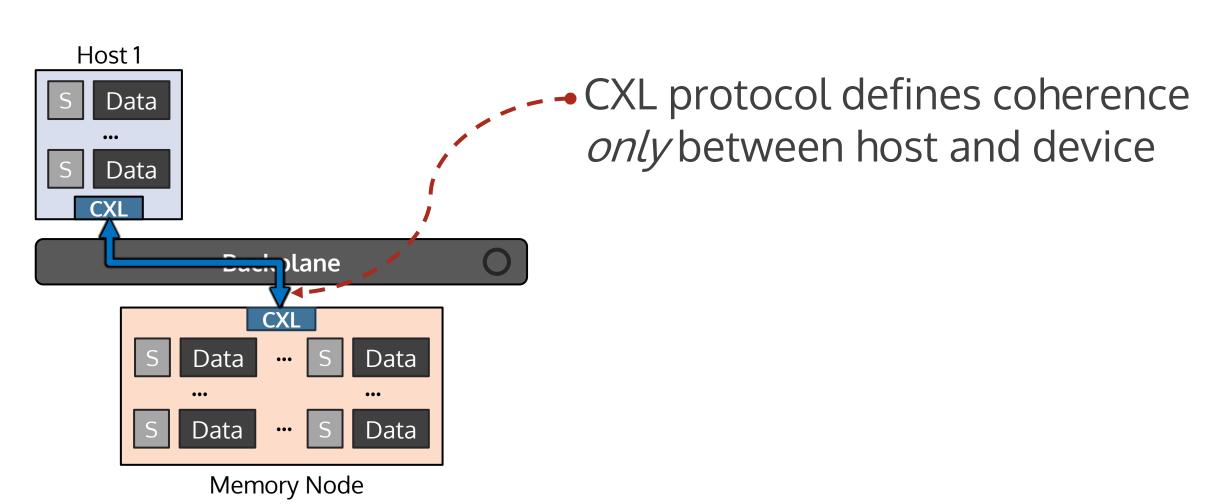

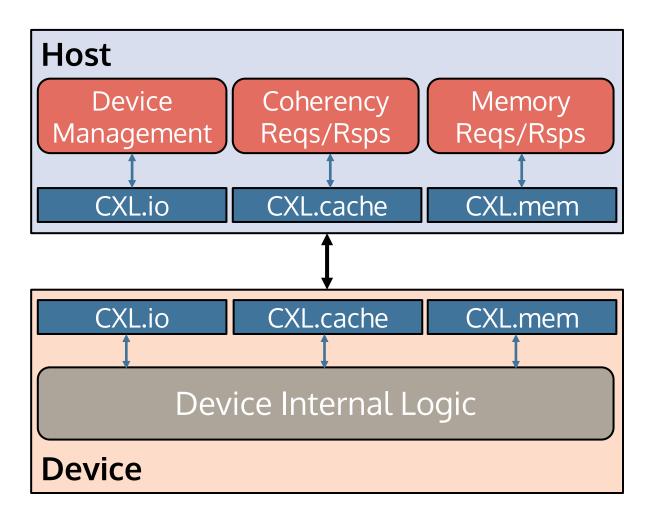

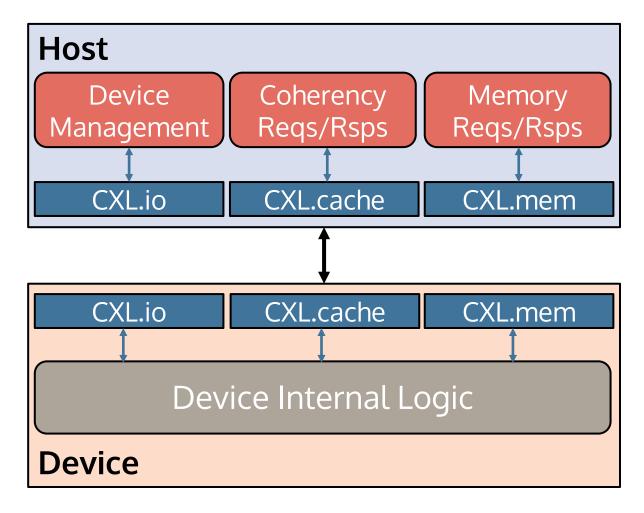

#### **CXL Protocols**

- 1. CXL.io

- Device Management

- 2. CXL.cache

- Coherency Management

- 3. CXL.mem

- Memory Read/Write

#### Goal 2: How to design a multi-host coherence control flow?

| Protocol  | Message  | Туре               |

|-----------|----------|--------------------|

| CXL.cache | RdOwn    |                    |

|           | RdAny    | Device Request     |

|           | CLFlush  |                    |

|           | GO-*     | Host Response      |

| CXL.mem   | MemRd    |                    |

|           | MemWr    | Host Poguest       |

|           | MemInv   | Host Request       |

|           | MemRdFwd |                    |

|           | Cmp-*    | Device<br>Response |

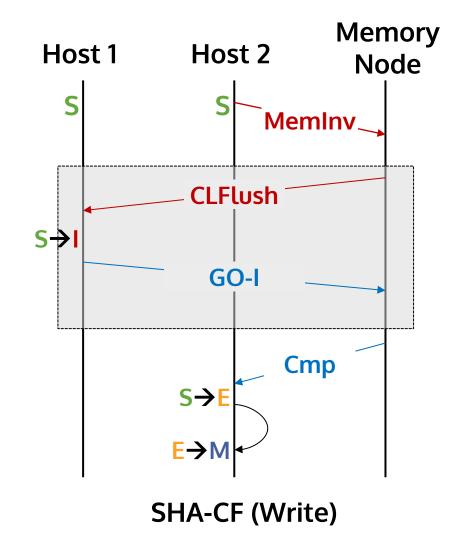

#### Goal 2: How to design a multi-host coherence control flow?

| Protocol  | Message  | Type               |

|-----------|----------|--------------------|

| CXL.cache | RdOwn    |                    |

|           | RdAny    | Device Request     |

|           | CLFlush  |                    |

|           | GO-*     | Host Response      |

| CXL.mem   | MemRd    |                    |

|           | MemWr    | Host Poquest       |

|           | MemInv   | Host Request       |

|           | MemRdFwd |                    |

|           | Cmp-*    | Device<br>Response |

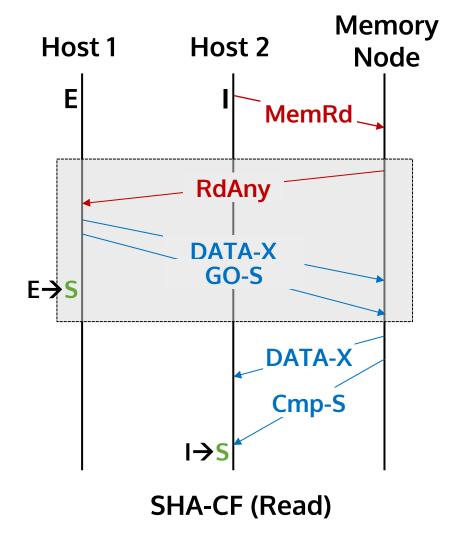

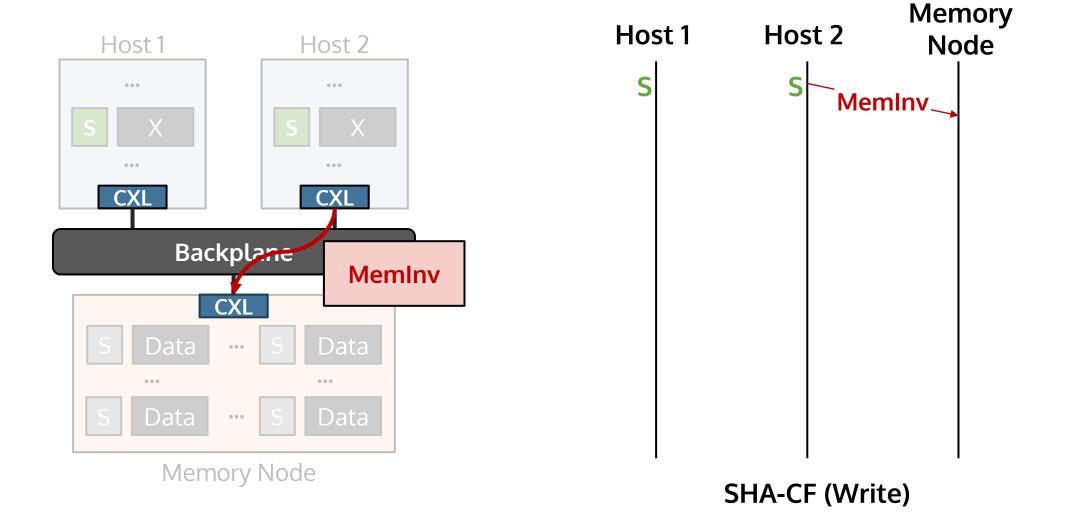

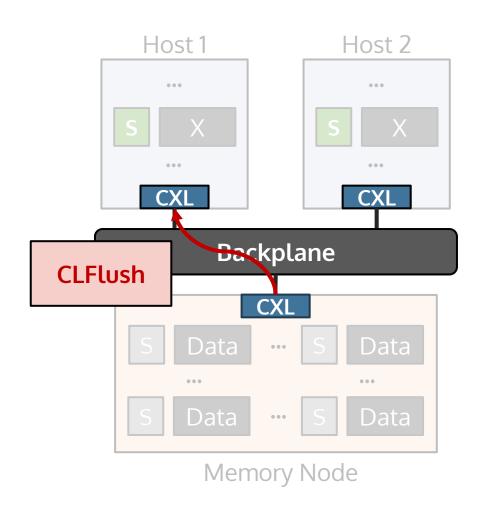

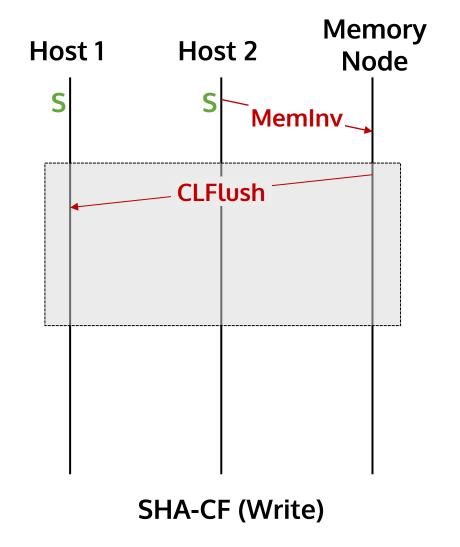

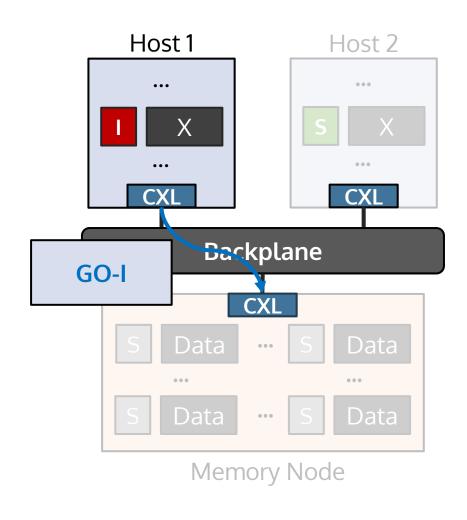

#### **CXL Protocols**

- A set of valid request/response pairs between Host and Device

- Design a sharing-enabled control flow strictly using the valid pairs

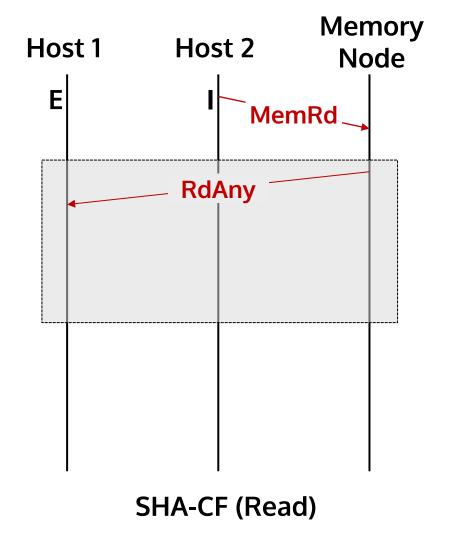

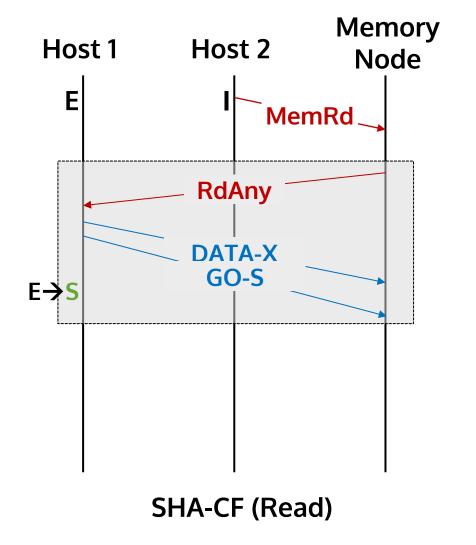

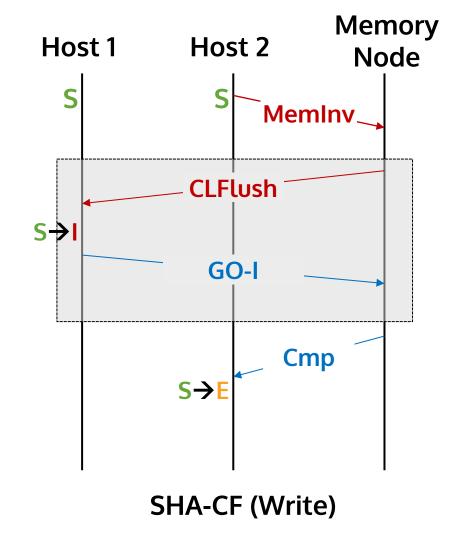

Goal 2: How to design a multi-host coherence control flow?

| PdOwn                         | Protocol | Message | Туре | CXL Protocols                                       |

|-------------------------------|----------|---------|------|-----------------------------------------------------|

| A set of valid request/respor |          | RdOwn   |      | <ul> <li>A set of valid request/response</li> </ul> |

Our Approach: Sharing-enabled Control Flow

Let's exploit CXL.cache messages

| CXL.mem | MemInv<br>MemRdFwd | Host Request       |

|---------|--------------------|--------------------|

|         | Cmp-*              | Device<br>Response |

#### **Outline**

- Introduction

- Motivation

- SDM: Sharing-enabled Disaggregated Memory System

- CXL-compatible Designs

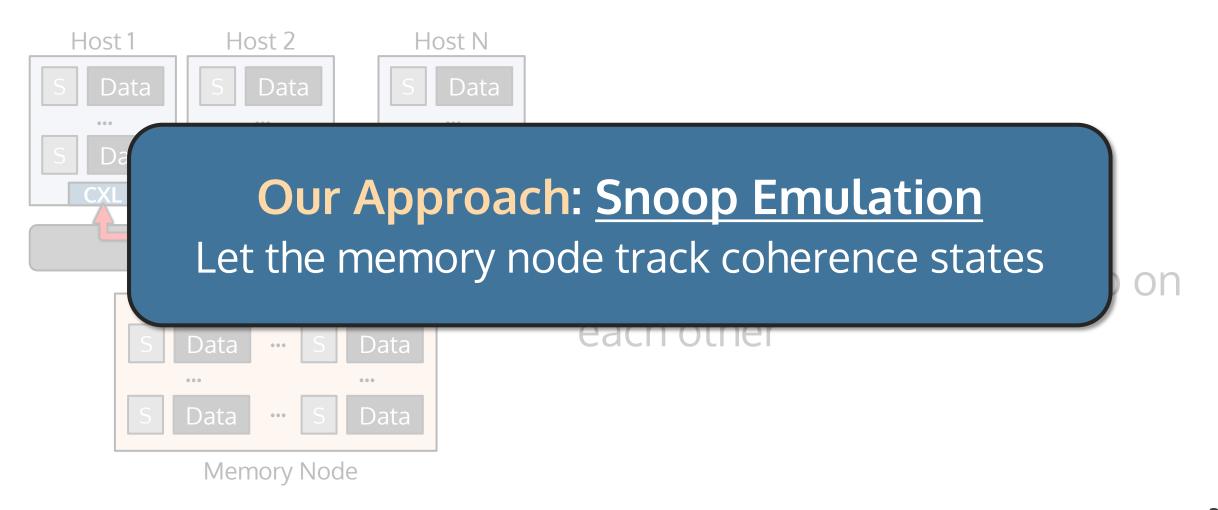

- Snoop Emulation

- CXL-compatible Control Flow

- Evaluation

- Conclusion

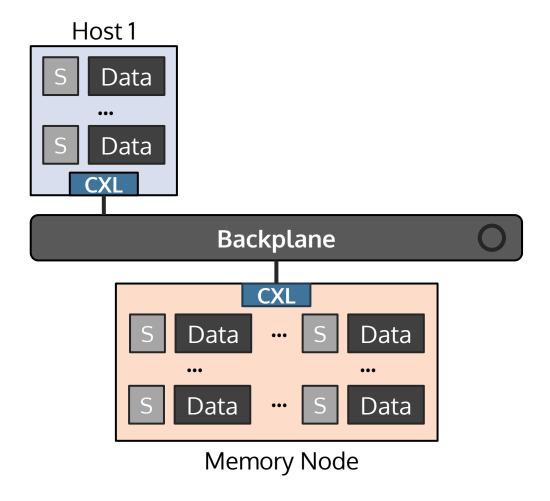

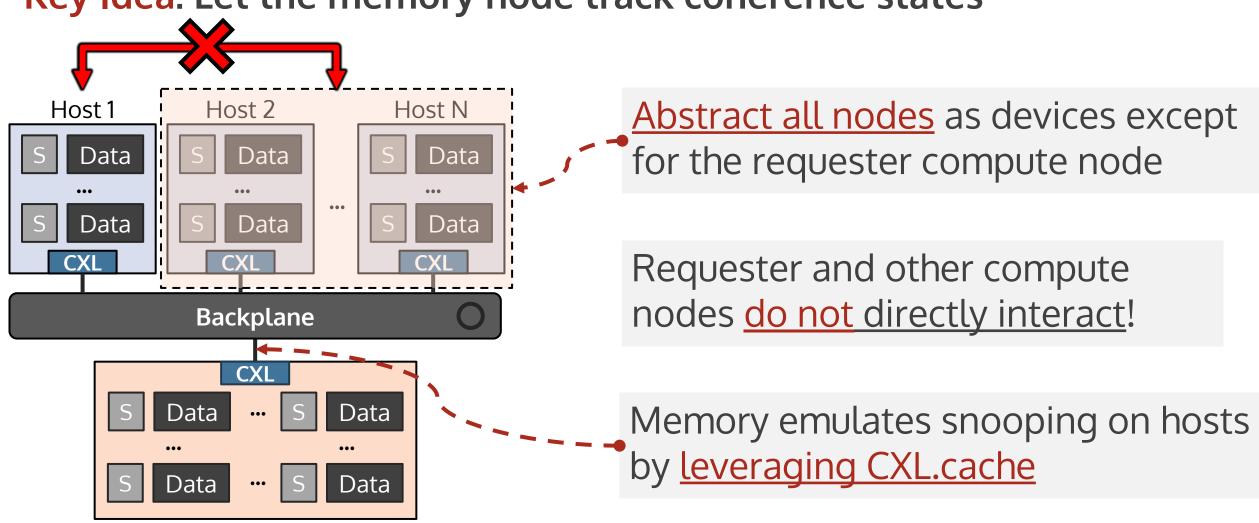

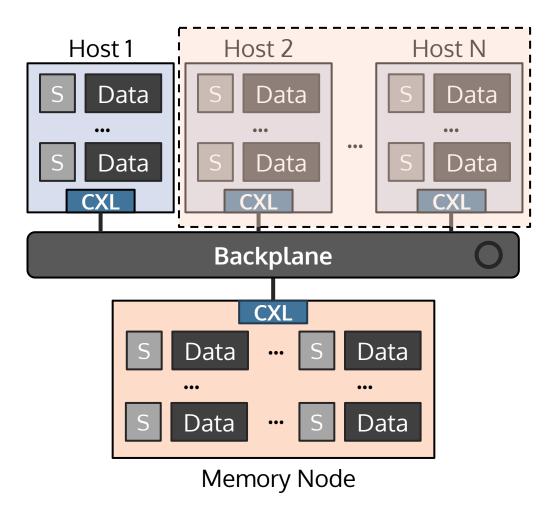

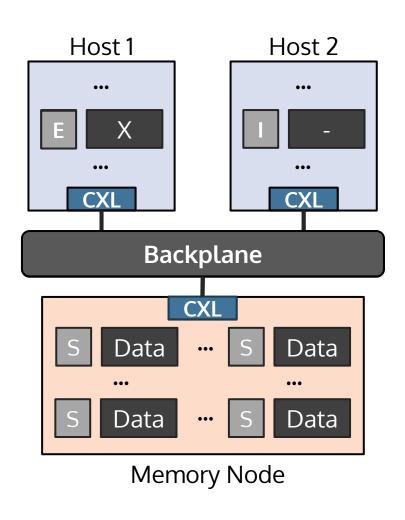

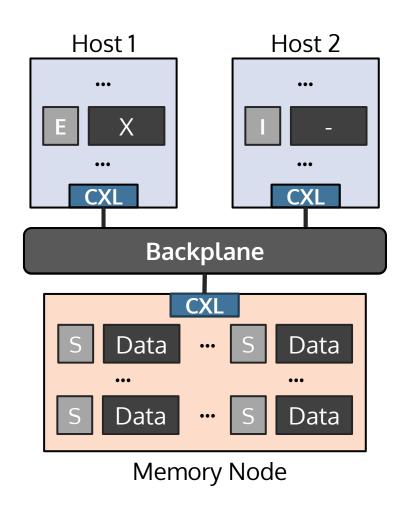

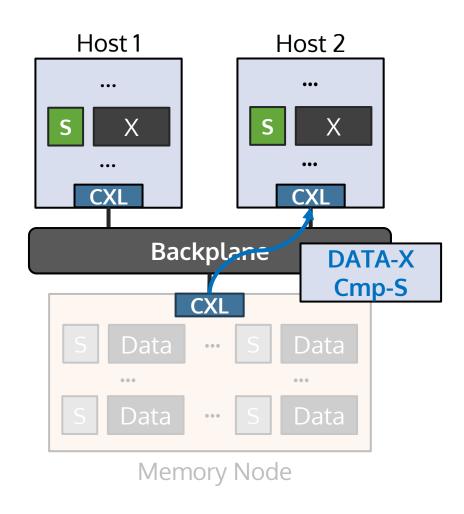

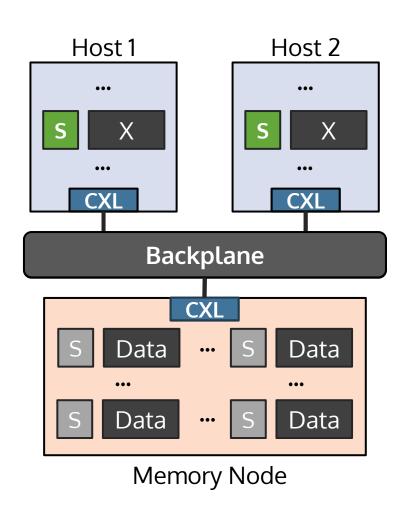

Memory Node

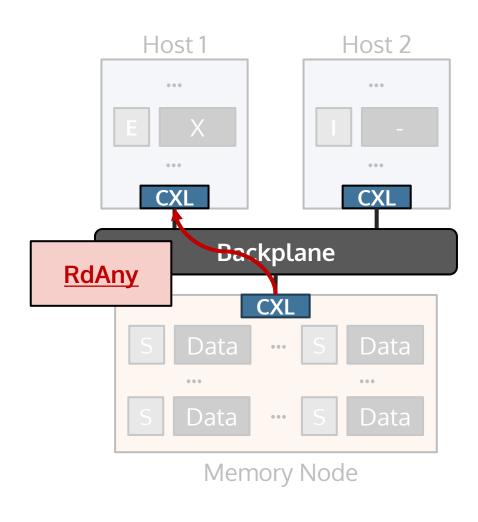

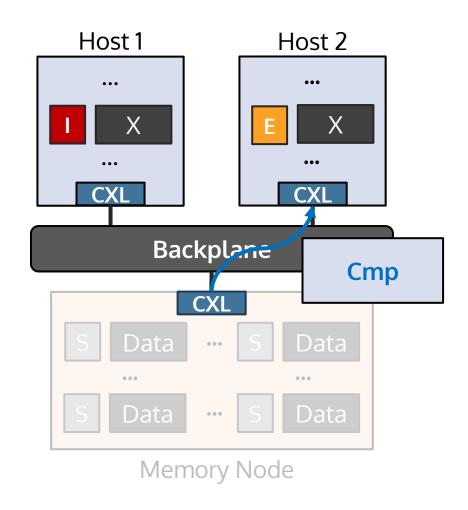

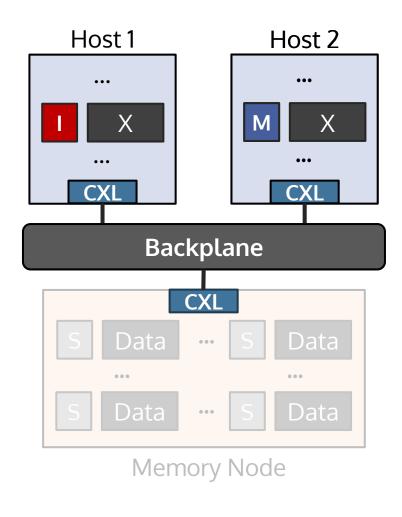

**Key Idea**: Let the memory node track coherence states

29

**Key Idea**: Let the memory node track coherence states

30

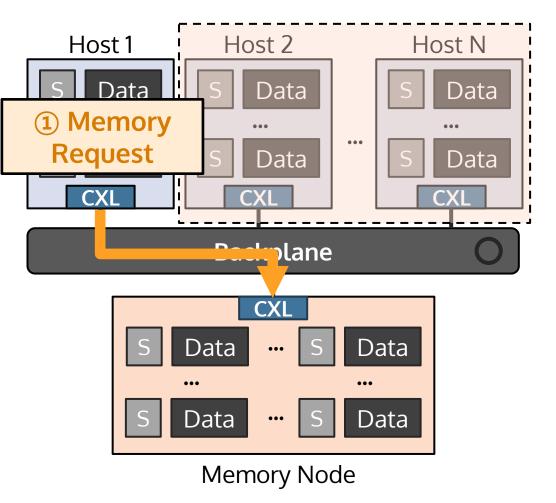

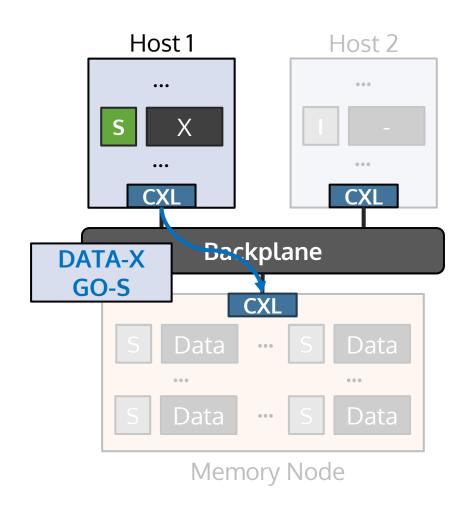

Key Idea: Let the memory node track coherence states

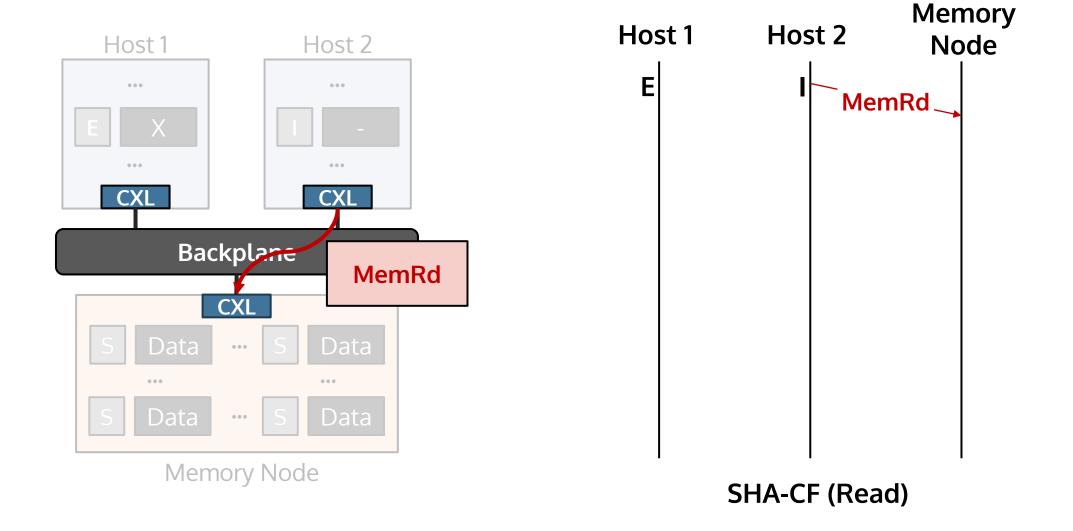

1. Memory Request from Host to Device

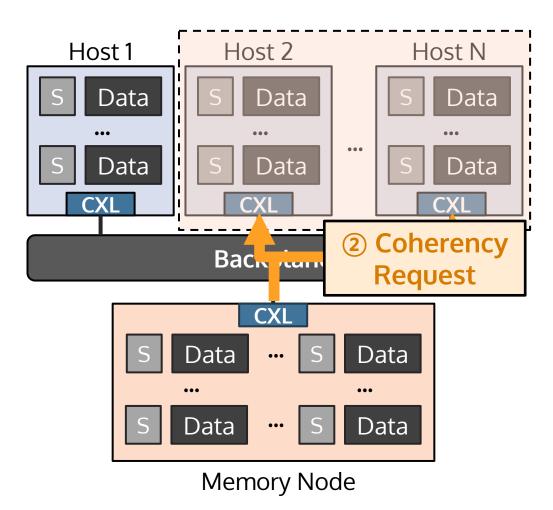

Key Idea: Let the memory node track coherence states

- 1. Memory Request from Host to Device

- 2. Coherency Request from Device to other Hosts

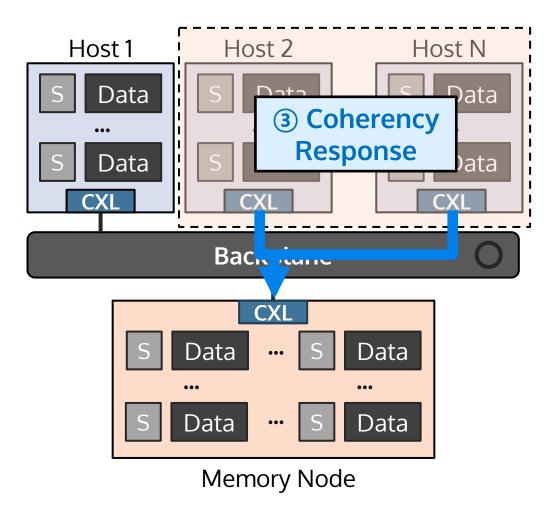

Key Idea: Let the memory node track coherence states

- 1. Memory Request from Host to Device

- 2. Coherency Request from Device to other Hosts

- 3. Coherency Response from other Hosts to Device

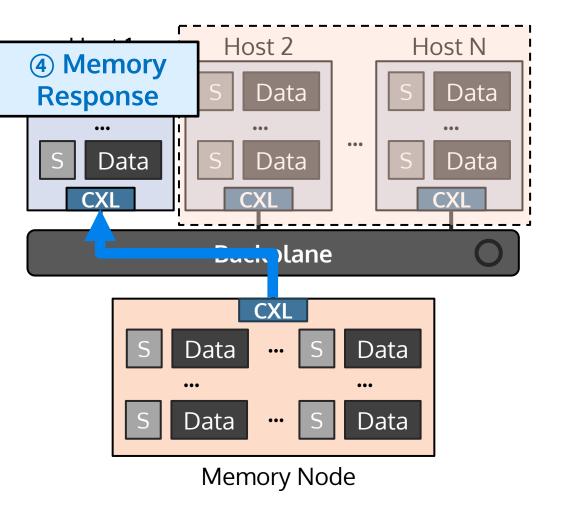

Key Idea: Let the memory node track coherence states

- 1. Memory Request from Host to Device

- 2. Coherency Request from Device to other Hosts

- 3. Coherency Response from other Hosts to Device

- 4. Memory Response from Device to Host

Memory Node

Key Idea: Let the memory node track coherence states

35

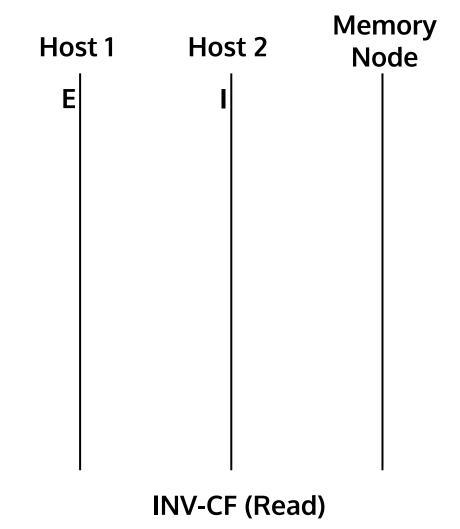

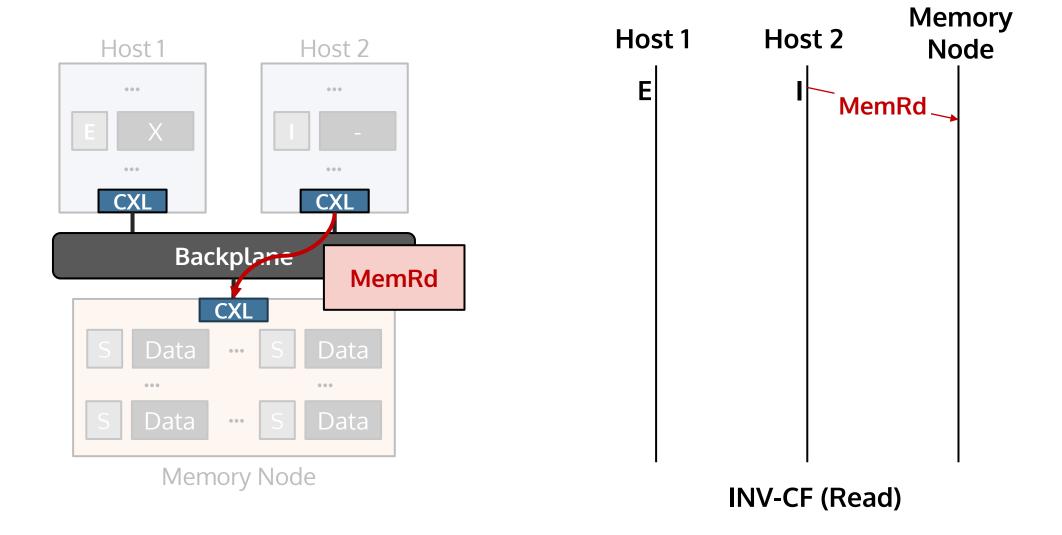

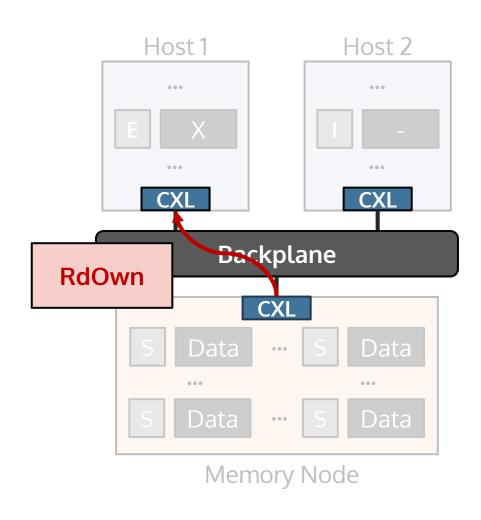

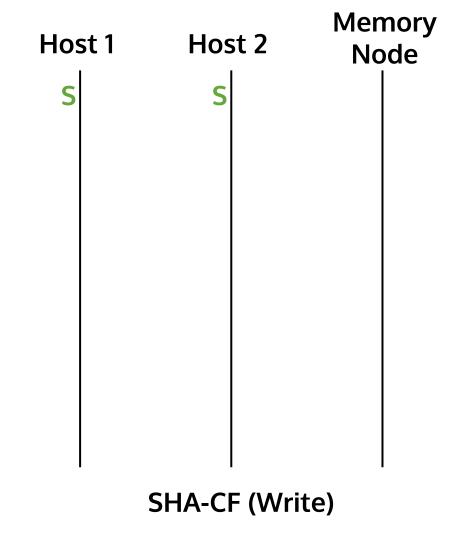

#### **CXL-compatible Control Flow**

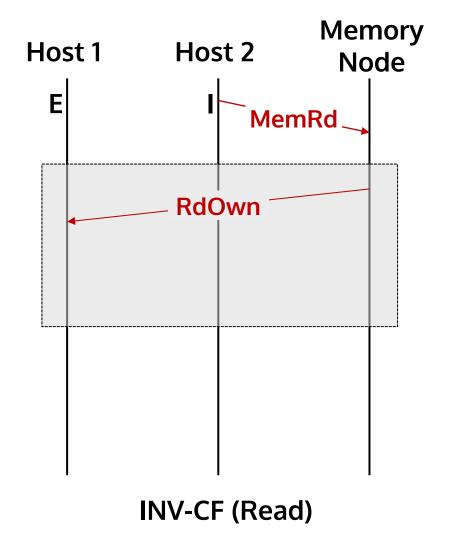

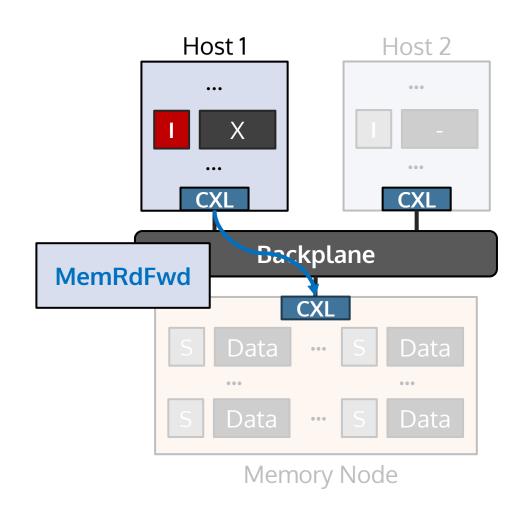

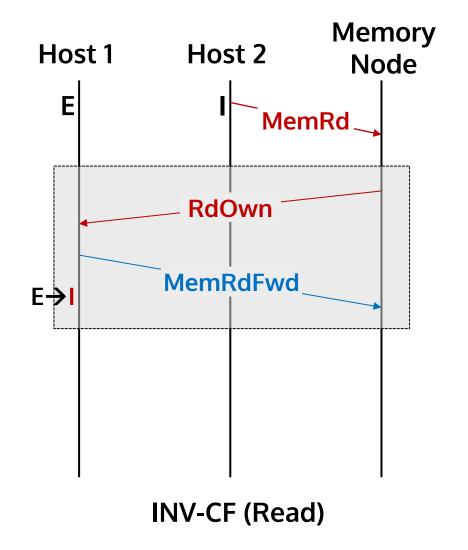

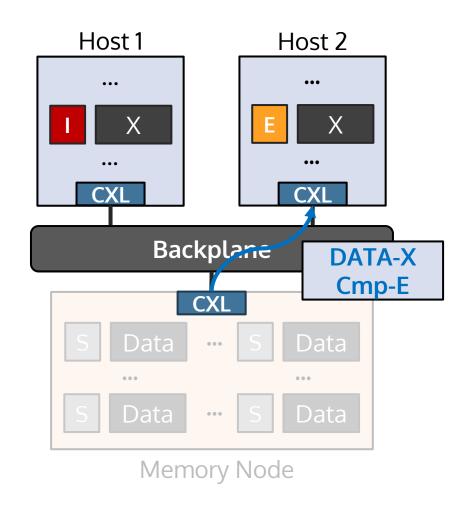

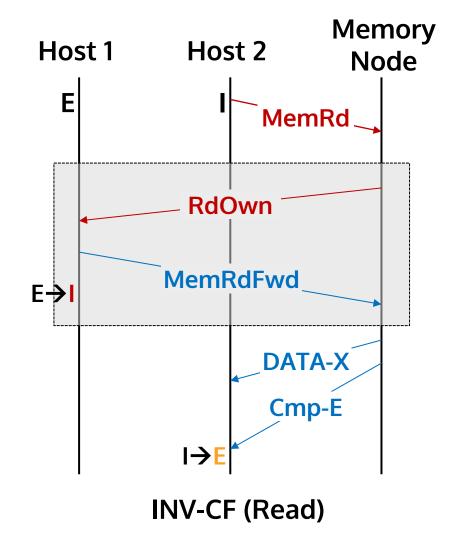

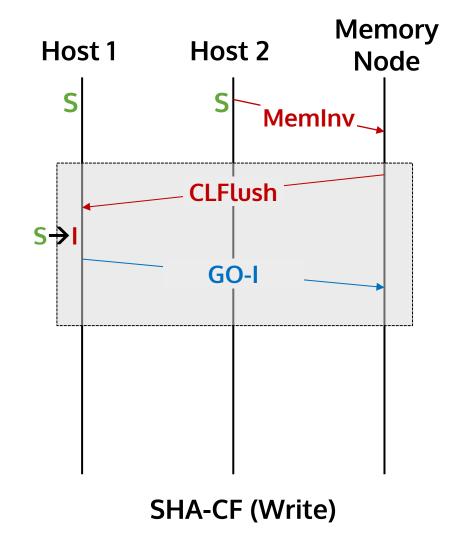

Straightforward: Invalidation-based Control Flow (INV-CF)

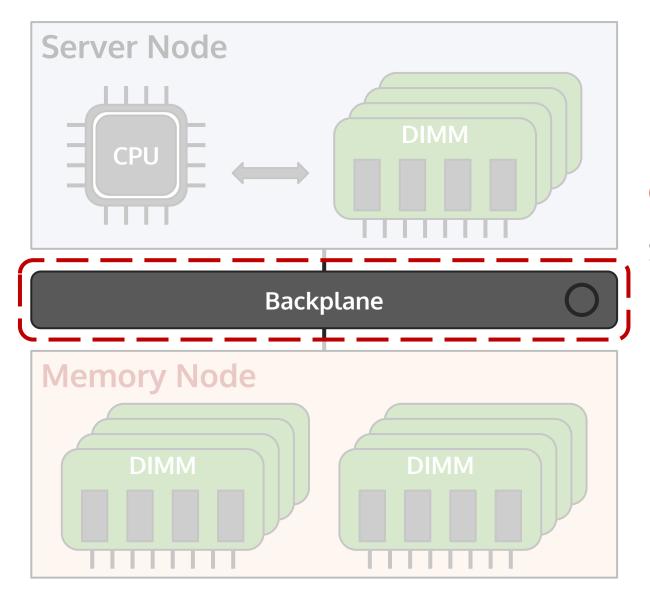

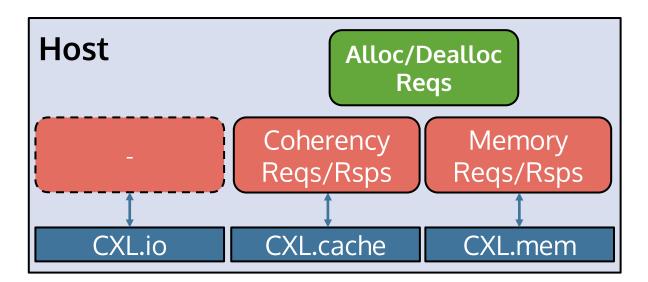

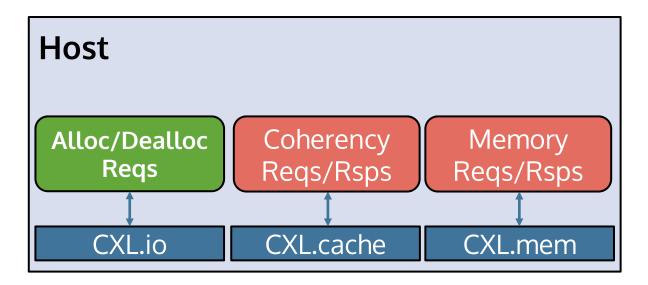

## **CXL-compatible Memory Management**

Q: How to allocate/deallocate pages from disaggregated memory?

#### Requirement

Alloc/Dealloc messages should not interfere with RD/WR requests

#### Our Approach

• Define a new message using <u>byte-15</u> of <u>CXL.io vendor-defined</u> message fields

## **CXL-compatible Memory Management**

Q: How to allocate/deallocate pages from disaggregated memory?

#### Requirement

Alloc/Dealloc messages should not interfere with RD/WR requests

#### Our Approach

• Define a new message using <u>byte-15</u> of <u>CXL.io vendor-defined</u> message fields

## **CXL-compatible Memory Management**

Q: How to allocate/deallocate pages from disaggregated memory?

#### Requirement

Alloc/Dealloc messages should not interfere with RD/WR requests

#### Our Approach

• Define a new message using <u>byte-15</u> of <u>CXL.io vendor-defined</u> message fields

|          | +0           |      | +1  |  |              |                 | +2           |          |    |              | +3     |

|----------|--------------|------|-----|--|--------------|-----------------|--------------|----------|----|--------------|--------|

| Byte 0>  | Fmt          | Type | R T |  | A<br>tt<br>r | L T<br>N H      | T E<br>P P   | Att<br>r | AT |              | Length |

| Byte 4>  | Requestor ID |      |     |  |              | Tag             |              |          |    | Message Code |        |

| Byte 8>  | Reserved     |      |     |  |              | Vendor ID = CXL |              |          |    |              |        |

| Byte 12> | Reserved     |      |     |  |              |                 | CXL VDM Code |          |    |              |        |

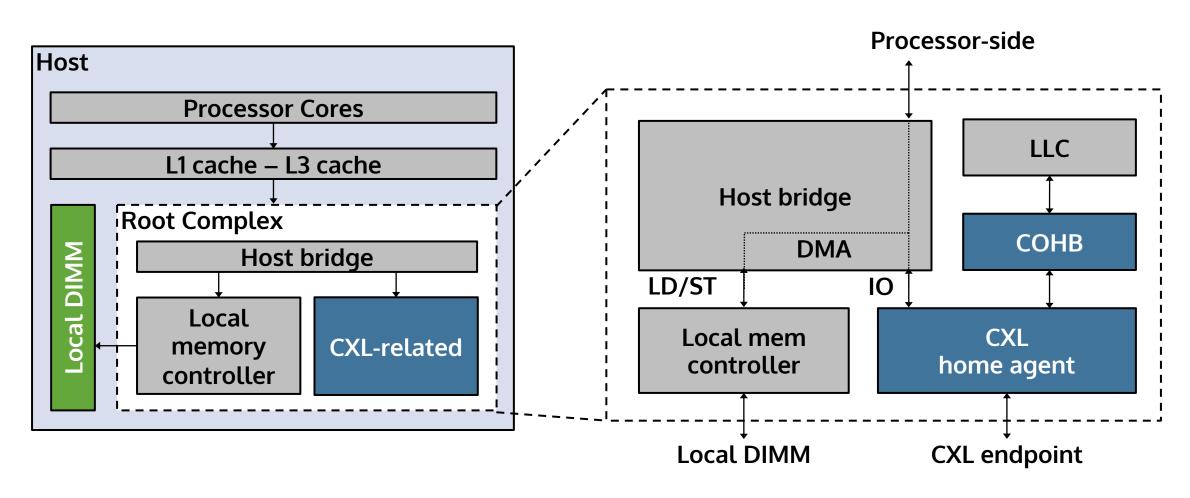

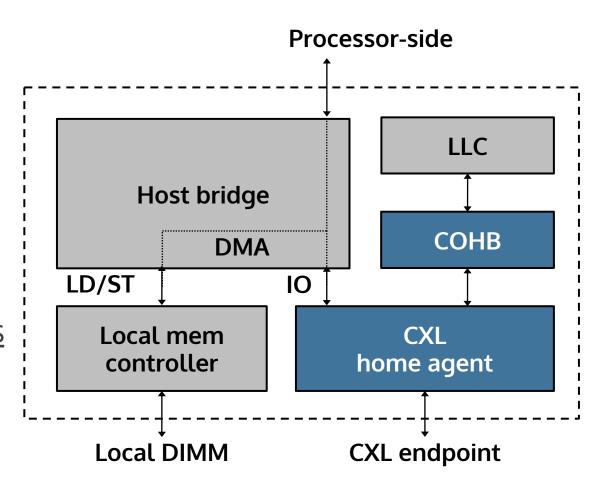

### **SDM Architecture**

#### Host-side CXL-compatible hardware

#### **SDM Architecture**

#### Host-side CXL-compatible hardware

### Coherence Bridge (COHB)

Manage system-level directory

#### CXL Home Agent

Generate coherence messages

#### **Our Extension**

• Generate <u>allocate/deallocate messages</u>

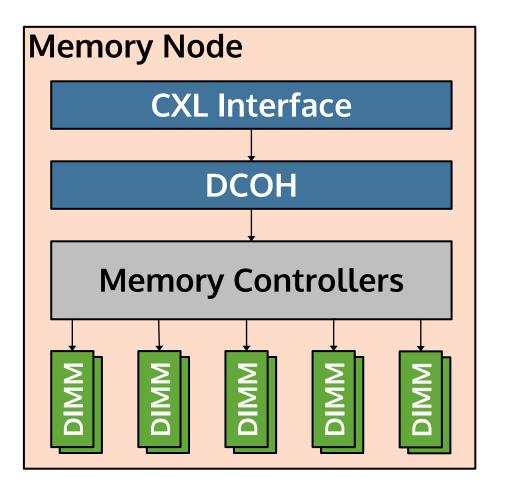

### **SDM Architecture**

#### Device-side CXL-compatible hardware

#### Device Coherency Agent (DCOH)

- Generates CXL.cache messages

- Can have a snoop filter

#### Our Extension

Send snoop messages to abstracted hosts

### More Discussions in the Paper

- Snoop Emulation

- Sharing-enabled Control Flow

- Memory Management Mechanism

- SDM Architecture

- Address Translation Mechanism

- How to implement it with CXL.io messages

- Speculative Access

- How to overcome the overhead of access control check

### **Outline**

Introduction

Motivation

- SDM: Sharing-enabled Disaggregated Memory System

- CXL-compatible Designs

- Evaluation

Conclusion

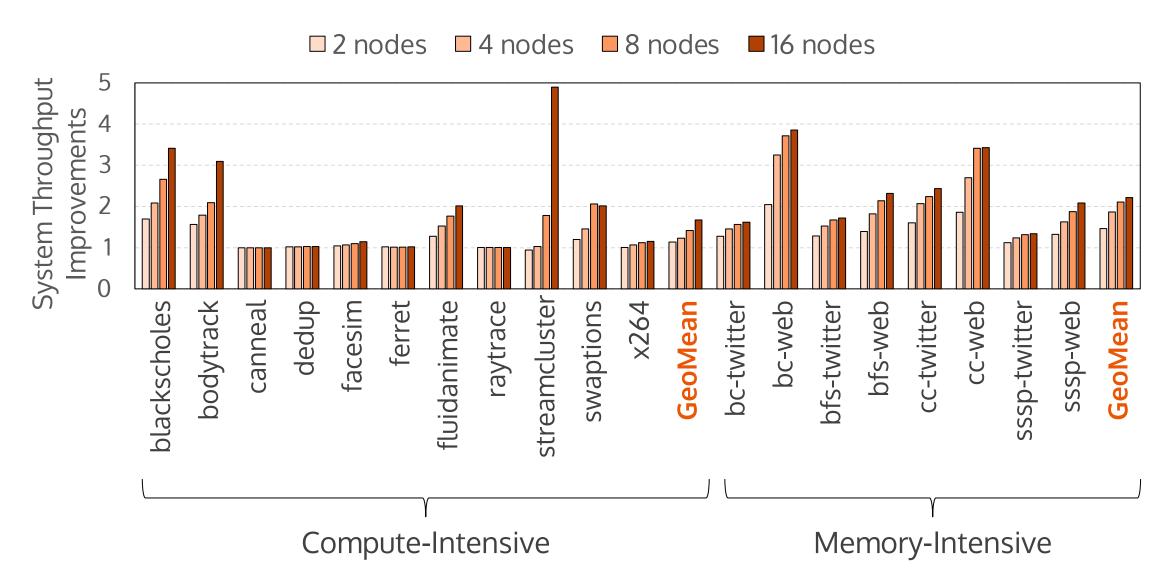

## Methodology

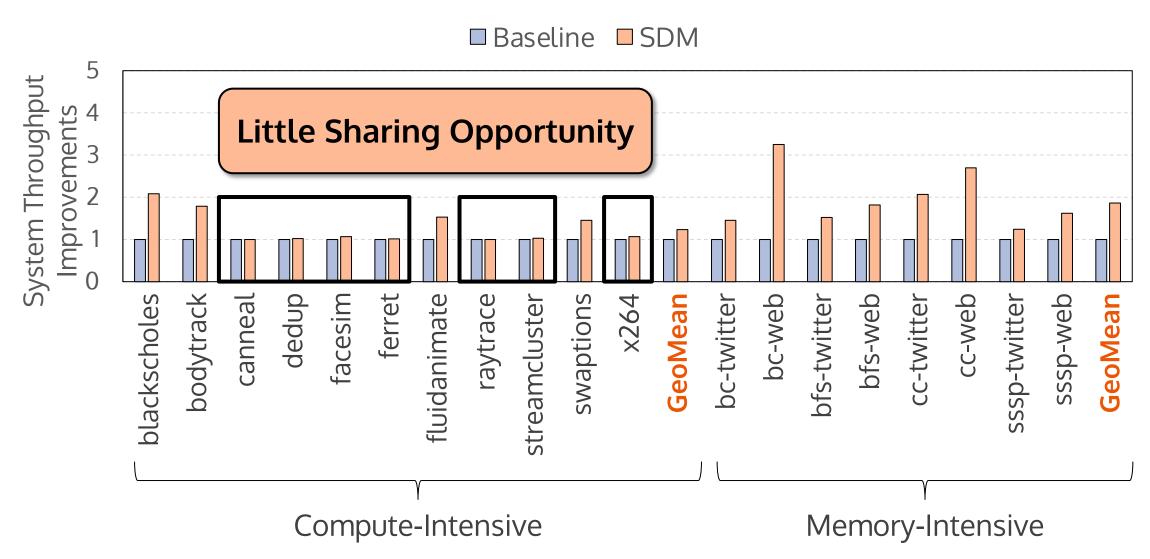

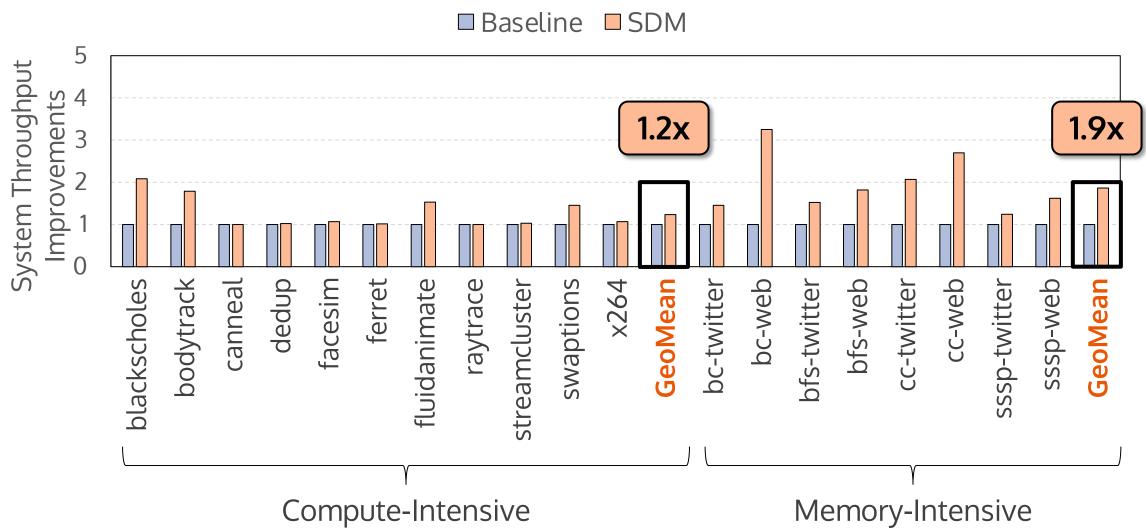

#### **Performance Evaluation**

In-house simulator using Intel PIN tool

#### **Evaluated Workloads**

- PARSEC (Compute-intensive)

- Intel GAP (Memory-intensive)

#### Baseline

• INV-CF: CXL 3.0-like invalidation-based control flow

#### **System Parameters**

| System        |                                  |  |  |  |  |

|---------------|----------------------------------|--|--|--|--|

| Configuration | 4 Compute Nodes<br>1 Memory Node |  |  |  |  |

| Compute Node  |                                  |  |  |  |  |

| Core          | 8 cores                          |  |  |  |  |

| L1 Cache      | 8-way, 32KB, 1ns                 |  |  |  |  |

| L2 Cache      | 4-way, 256KB, 4ns                |  |  |  |  |

| L3 Cache      | 16-way, 2MB, 40ns                |  |  |  |  |

| Memory Node   |                                  |  |  |  |  |

| Latency       | 80ns                             |  |  |  |  |

| Interconnect  |                                  |  |  |  |  |

| Latency       | 500ns                            |  |  |  |  |

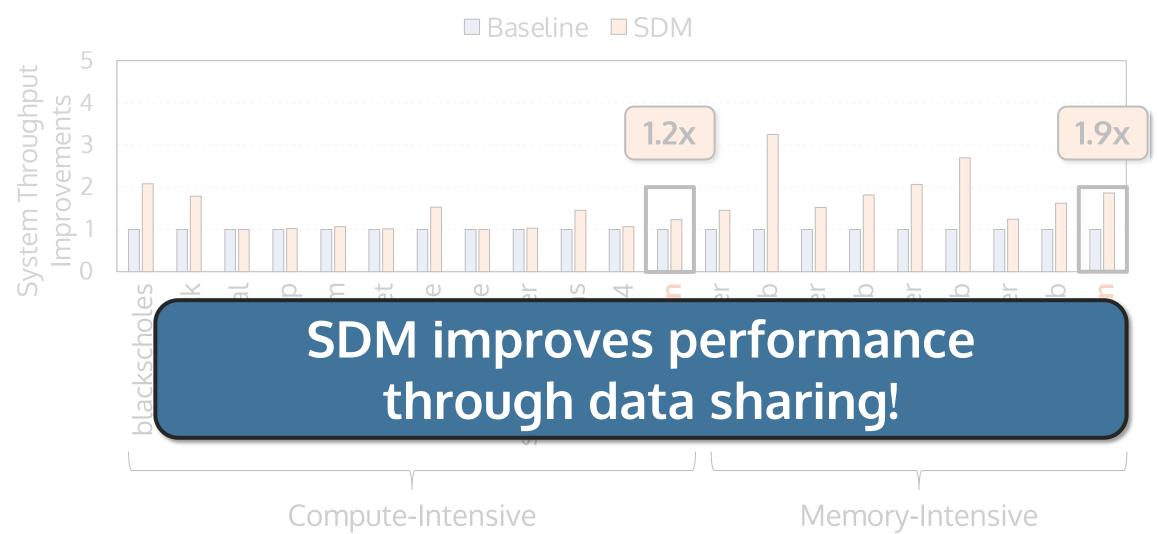

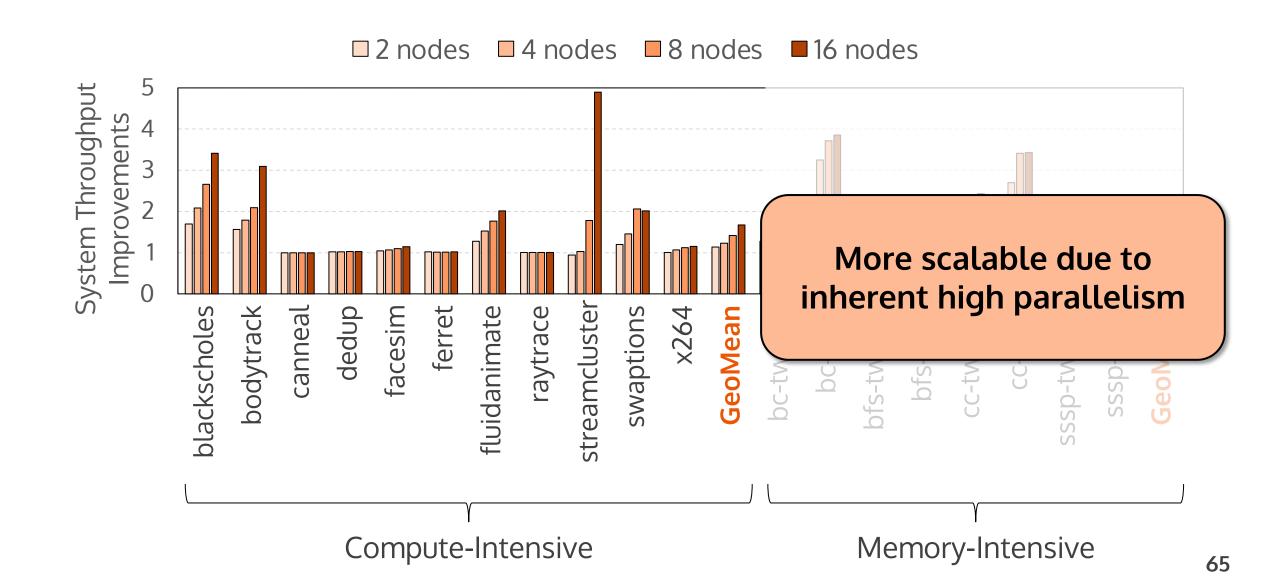

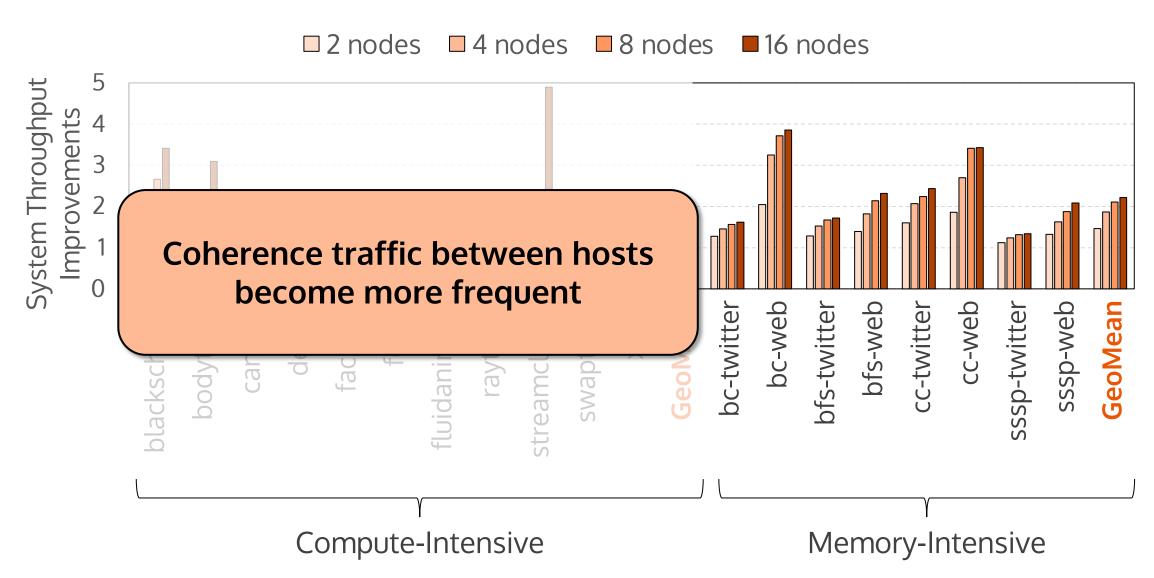

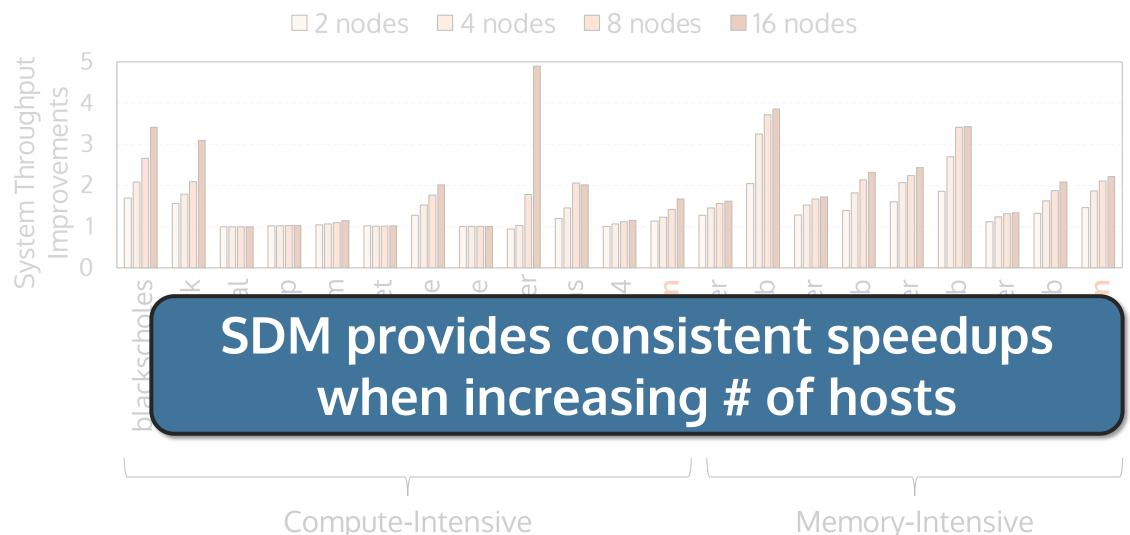

### **Performance**

### **Performance**

### **Performance**

### **Outline**

Introduction

Motivation

- SDM: Sharing-enabled Disaggregated Memory System

- CXL-compatible Designs

- Evaluation

Conclusion

#### Conclusion

#### Goal

Design a CXL-compatible, Sharing-enabled Disaggregated Memory System

#### **Solution**

- Snoop Emulation enables multi-host coherence management

- SHA-CF enables data sharing between multiple hosts

#### Result

SDM achieves an average of 1.5x speedup over naïve CXL-based disaggregated memory systems

# Thank You!